实验性纳米片材料标志着迈向下一代低功耗高性能电子产品的一步

中国的一组研究人员已经开发出一种高导电率材料,可以大大降低电子和光电微芯片关键部分的接触电阻和肖特基势垒高度,为计算机和数字成像元件的功耗与性能相比铺平了道路现有的芯片组。

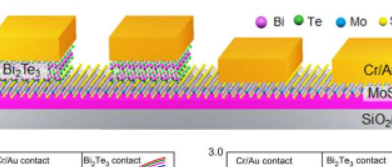

二硫化钼(MoS2)材料非常薄,属于二维类。也就是说,它生长在沿X和Y两个方向延伸的薄片中,但在Z轴上几乎无法测量,因为材料通常只有一个分子或原子的高度。

由湖南大学材料科学与工程学院李东教授和潘安联教授领导的团队在《纳米研究》上发表了他们的研究成果。

在文章“EpitaxialvanderWaalsContactsforLowSchottkyBarrierMoS2FieldEffectTransistors”中,作者强调了二维材料如何因其丰富且可调的电子态以及多样化的光学、电子和机械特性而引起了极大的关注,这使它们成为未来高性能电子和光电设备(例如晶体管、光电探测器和发光二极管)的有前途的构建模块。

该实验是为了解决问题。“二维半导体晶体管的性能主要依赖于芯片内元件之间的微观连接,而这些连接的质量最终取决于这些接触点所使用的材料,这些材料通常是通过热蒸发获得的金属,限制了其性能基于二维材料的晶体管,”李说。

为了开发更高性能的接触点,Li的团队使用了碲化铋(Bi2Te3),这是一种高导电性准金属和半金属,与半导体MoS2相结合。将这些类金属纳米片晶体作为混合物生长在一起,最初产生了有希望的结果。

“近年来,实现外延生长半导体接触的尝试在实验室环境中取得了成功,但不太可能扩大到制造芯片和其他设备所需的水平,”李说。

“这些方法大多对材料制备和制造提出了严格的要求,与集成电路的进一步制造工艺难以兼容。同时实现高质量的半导体二维材料和良好的接触对于可靠的器件应用至关重要。“

制造这种实验性范德瓦尔斯接触的过程涉及在两步合成过程中垂直堆叠MoS2和Bi2Te3。随着MoS2单层的生长,三氧化钼(MoO3)粉和硫粉分别放在炉子的中心和上游,一块二氧化硅(SiO2)衬底放在石英管的下游.

对于Bi2Te3纳米片的第二步生长,将Bi2Te3粉末和生长的MoS2纳米片分别放置在石英管的中心和下游。生长5分钟后,获得MoS2/Bi2Te3异质结构。

研究人员观察到,生长过程中的生长温度和气体流速会影响Bi2Te3纳米片的厚度和成核位置。

该团队使用各种电气和成像技术来观察混合纳米片的外观和导电性能,发现新的接触方法大大优于金接触,由于金在芯片制造中的普遍性,金接触可用作基线测量。

新的接触方法在不同的环境温度下进行了测试,并在室温下保持了良好的性能——这是使MoS2/Bi2Te3半导体接触方法成为未来商业可行性的良好候选者的一个重要里程碑。

“结合多重优势,外延范德瓦尔斯Bi2Te3触点为二维MoS2在未来光电器件中的应用提供了新的策略,”李说。

“既然我们已经在受控实验室环境中建立了Bi2Te3触点的功能,接下来的步骤将是继续研究和优化这种方法,希望这项新技术最终能够被广泛应用于更强大、能耗更低的电子产品。”

声明:本站所有文章资源内容,如无特殊说明或标注,均为采集网络资源。如若本站内容侵犯了原著者的合法权益,可联系本站删除。